Meet Diverse Functional and Safety Requirements with Multicore Processors

Contributed By DigiKey's North American Editors

2020-10-01

Automotive, industrial, robotics, building control, and other critical embedded system applications are expected to take on more diverse workloads extending from low-power real-time monitoring to high-level multimedia applications with multiscreen graphics displays for human-machine interfaces (HMIs). While meeting these broad functional requirements they must also be able to support stringent safety standards, lower cost and footprint, and optimize the power/performance balance.

To meet these often sometimes conflicting requirements, developers have to date been forced to either sacrifice functional capability or complicate design and manufacturing with added devices needed to support specific requirements for graphics, security, and safety, among others. What developers really need is a single solution able to support a wide range of products that meet these requirements across a wide range of critical embedded system applications.

This article quickly describes the evolution of critical embedded system design. It will then show how multicore application processors—designed specifically by NXP Semiconductors to support a fast-expanding list of requirements for both broad functionality and safety certifiable capabilities—can be used to address developers’ challenges.

The evolution of embedded system design considerations

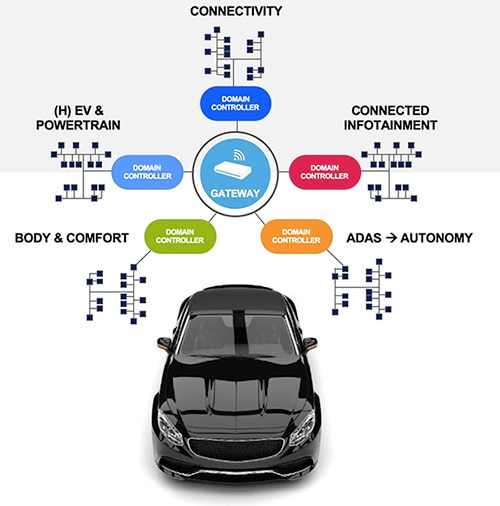

The traditional role of embedded devices in supporting a limited set of system functions has been largely replaced by demand for devices providing broad capabilities. In industrial applications, for example, the need for enhanced HMI capabilities in smart tools and equipment calls for processors able to deliver optimized graphics while meeting more traditional industrial real-time requirements. Similarly, the trend in automotive applications toward hierarchical architectures comprising functional domain clusters and gateways drives a need for processors fully able to meet those requirements (Figure 1).

Figure 1: The trend toward more hierarchical automotive systems architectures has created a need for more integrated, scalable processor solutions. (Image source: NXP Semiconductors)

Figure 1: The trend toward more hierarchical automotive systems architectures has created a need for more integrated, scalable processor solutions. (Image source: NXP Semiconductors)

Within each functional domain, demand for more sophisticated capabilities continues to raise the threshold for performance and integrated capabilities. For example, the emergence of heads-up displays demands solutions able to ensure continued delivery of vital graphical information to drivers. Along with these next-generation displays, the growing need for enhanced driver awareness adds additional requirements for camera interfaces and high-performance execution of advanced recognition software able to provide drowsiness detection.

As applications continue to evolve, the need for highly integrated, scalable solutions becomes more urgent to meet increasingly diverse requirements while minimizing design footprint, cost, and complexity. Using NXP's i.MX 8 family of application processors, developers can leverage a compatible platform of processors with the range of capabilities and performance needed to support a broad range of application requirements. Within the i.MX 8 family, the NXP i.MX 8X series addresses emerging needs for safety certifiable processors required in mid-range automotive and industrial applications.

Multicore architecture manages diverse workloads

One of the difficulties developers face in implementing devices for automotive and industrial applications is the sheer breadth of requirements. Where developers could expect to deal with either real-time or high-level application processing workloads, the demand for intelligent subsystems has merged these significantly different types of computing. Increasingly, developers need solutions capable of delivering both reliable real-time response and high-performance application execution while supporting functional safety requirements.

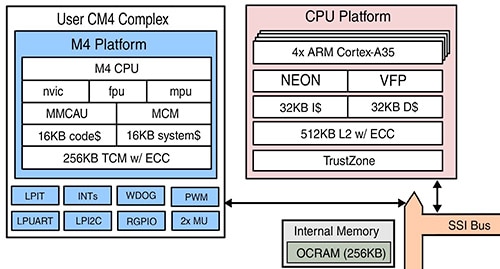

Designed to deliver real-time capabilities, high-performance processing, and low power consumption, NXP i.MX 8X series processors take full advantage of a sophisticated multicore central processing unit (CPU) architecture to manage diverse computational workloads (Figure 2).

Figure 2: The NXP i.MX 8X series uses a multicore architecture comprising an Arm Cortex-M4 (CM4) embedded processor and multiple Arm Cortex-A35 application processors to support mixed software workloads. (Image source: NXP Semiconductors)

Figure 2: The NXP i.MX 8X series uses a multicore architecture comprising an Arm Cortex-M4 (CM4) embedded processor and multiple Arm Cortex-A35 application processors to support mixed software workloads. (Image source: NXP Semiconductors)

For general purpose real-time processing tasks, i.MX 8X devices include an Arm Cortex-M4 (CM4) processor with floating point unit (FPU), memory protection unit (MPU), memory-mapped cryptographic acceleration unit (MMCAU), and miscellaneous control module (MCM). To support external peripherals like sensors and actuators, this user CM4 complex combines a nested vector interrupt controller (NVIC) with a comprehensive set of interfaces and modules, including low-power periodic interrupt timer (LPIT), pulse width modulation (PWM), and other functions commonly required in automotive and industrial applications. A pair of cache memories and tightly coupled memory (TCM) with error correcting code (ECC) capability helps minimize external memory access, speed execution, and deal with memory errors.

For rapid execution of application workloads, the CPU platform comprises multiple power efficient Arm Cortex-A35 application processors (APs)—two APs in 8DualXPlus processors such as the MIMX8UX6AVLFZAC, and four APs in 8QuadXPlus processors such as the MIMX8QX6AVLFZAC. Along with dedicated instruction (I$) and data (D$) cache, the CPU platform includes a shared 512 kilobyte (Kbyte) level 2 (L2) cache with ECC.

The architecture's Arm Cortex-A35 cores provide both software compatibility and performance scalability, supporting both 32-bit backward compatibility and 64-bit performance. To further speed execution of compute-intensive algorithms such as signal processing and machine learning, the Arm Cortex-A35 processors provide vector floating point (VFP) processing and Arm's Neon single instruction multiple data (SIMD) architecture extensions. To accelerate execution of software for image processing, computer vision, and machine learning, the Arm Compute Library offers functions optimized for Arm processor and graphics processing unit (GPU) architectures, and the open source Ne10 C library provides Arm-optimized functions for compute-intensive operations.

Dedicated engines offload primary CPUs

In addition to the user CM4 complex and Arm Cortex-A35 multicore CPU platform, the architecture provides additional dedicated engines for multimedia applications. Along with a digital signal processor (DSP) for audio and voice codec processing, the architecture integrates both a GPU and a video processing unit (VPU). The device's GPU supports standard graphics libraries, accelerating operations using four separate four-component floating point vectors (vec4) with 16 execution units and a high performance, two-dimension bit blit engine. The VPU handles popular video formats, accelerating decoding up to 4Kp30 (progressive, 30 Hz) and encoding up to 1080p30. In turn, the chip's dedicated display controller block can drive graphics output to as many as three independent displays.

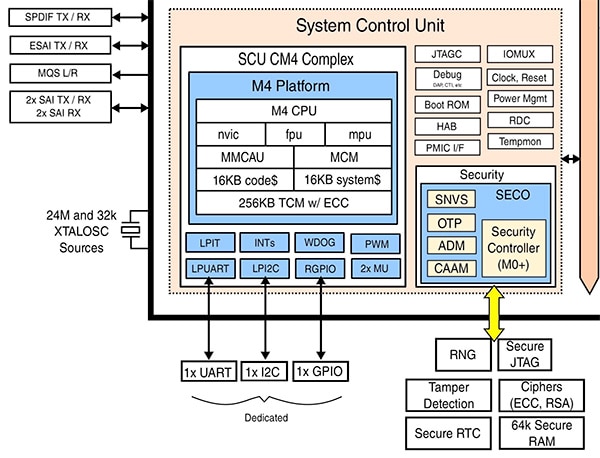

To further maximize performance, the i.MX 8X architecture also integrates additional processor cores designed to free the primary CPU platforms from the additional processing load typically incurred in executing system management and security services. For system management, the architecture's system control unit (SCU) integrates a CM4 complex that matches the user CM4 complex but remains dedicated completely to SCU operations and unavailable for use by developers (Figure 3).

Figure 3: Integrated deep within NXP i.MX 8X processors and unavailable to developers, the SCU uses a dedicated Arm Cortex-M4 (CM4) subsystem to offload system management tasks from the device's main processors. (Image source: NXP Semiconductors)

Figure 3: Integrated deep within NXP i.MX 8X processors and unavailable to developers, the SCU uses a dedicated Arm Cortex-M4 (CM4) subsystem to offload system management tasks from the device's main processors. (Image source: NXP Semiconductors)

Along with managing power, clocking and other internal functions, the SCU controls pin multiplexing and input/output (I/O) channel drive strength in normal operation. In fact, the user CM4 complex and Arm Cortex-A35 APs cannot directly access these various low-level hardware capabilities. Instead, the SCU serves to abstract these capabilities, so software running on the user CM4 or APs simply needs to call SCU firmware application programming interface (API) functions to perform functions such as powering down unneeded power domains. If that power domain is being shared with another processor, for example, the SCU simply acknowledges the power-down request but keeps the domain powered until that other processor issues a power-down request as well.

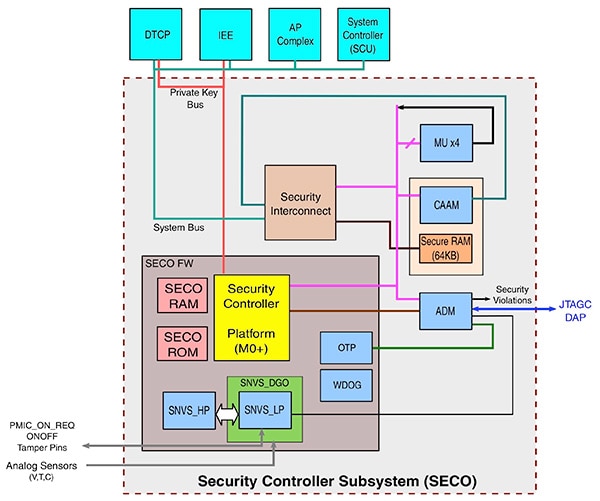

To manage the i.MX 8X device's extensive security support, another dedicated processor comes into play in the device's security controller (SECO) subsystem. Within the SECO subsystem, an integrated low-power Arm Cortex-M0+ processor executes firmware that supports hardware based security capabilities, including a private bus access for secure keys, one-time programmable (OTP) memory for secure key storage, and secure non-volatile storage (SNVS) for additional private data or ephemeral keys (Figure 4).

Figure 4: Within the NXP i.MX 8X security controller (SECO) subsystem, a dedicated low-power Arm Cortex-M0+ processor manages security operations, drawing on a private key bus and multiple hardware modules for secure storage, cryptography acceleration, and authenticated debug access. (Image source: NXP Semiconductors)

Figure 4: Within the NXP i.MX 8X security controller (SECO) subsystem, a dedicated low-power Arm Cortex-M0+ processor manages security operations, drawing on a private key bus and multiple hardware modules for secure storage, cryptography acceleration, and authenticated debug access. (Image source: NXP Semiconductors)

Beyond these core security mechanisms, the SECO subsystem coordinates security operations for tamper detection and secure debug mediated through its Authenticated Debug Module (ADM). For secure execution, the integrated Cryptographic Acceleration and Assurance Module (CAAM) hardware security module supports a full suite of security algorithms including symmetric and asymmetric cryptography, hash functions, and a random number generator (RNG).

In normal operation, device processing units including the SCU, APs, and Digital Transport Content Protection (DTCP) accelerator use the SECO security interconnect to access CAAM functionality through the system bus. Other than access through CAAM direct memory access (DMA) functionality, the SECO's dedicated Cortex-M0+ processor cannot access the system bus. Instead, it uses protected internal connections to access peripherals, secure random access memory (RAM) and read-only memory (ROM), and its special private key bus.

Along with its use of the DTCP accelerator, this private key bus plays a central role in i.MX 8X processor support for on-the-fly encryption and decryption. Here, the security processor uses its resources to provide private keys needed by the device's Inline Encryption/Decryption Engine (IEE) module as it securely reads from or writes to encrypted storage, without involvement by the requesting processor, DMA controller, or I/O device.

Building on Arm's TrustZone technology integrated in the device's Cortex-A35 processors, the SECO subsystem also works with the SCU during the secure boot process. In this process, the SCU interprets boot settings, configures the boot sources, and loads boot images to internal or external memory. In turn, the SECO subsystem uses its cryptography functions to authenticate signed firmware images after they are loaded but before they are executed.

Safeguarding critical displays and control functionality

While the ability to process diverse workloads efficiently and securely is important, for mission critical applications such as those in automotive and industrial segments, the ability to safeguard key capabilities is equally vital. NXP's i.MX 8X family combines its processing capabilities with safety certifiable capabilities required to meet these critical requirements.

The processor family's safety support is built in at a number of levels, starting with fabrication in a fully depleted silicon on insulator (FD-SOI) process technology that enhances system reliability. Because system safety depends on a robust security foundation, the combination of TrustZone-enabled APs, the SECO subsystem, and secure boot capabilities can provide the kind of trusted environment needed to thwart threats to safety and security.

At the same time, the ability to independently handle time-critical tasks with the user CM4 complex and offload critical system tasks to the SCU and SECO subsystems helps ensure that mission critical application capabilities remain available despite varying processing load. In fact, NXP extends this concept to support for mission critical displays through the company's SafeAssure technology, which integrates an Automotive Safety Integrity Level B (ASIL B)-ready hardware display failover path in i.MX 8X devices. With SafeAssure, users are automatically provided with a failover image if the device detects a data integrity or GPU error. Running in the background, this failover image ensures that critical information remains available even during failure of the primary display.

Support for safety applications extends to memory access in i.MX 8X-based systems. Among their supported memory interfaces, i.MX 8X devices provide 8-bit ECC for Double Data Rate 3 low voltage (DDR3L) memory. Along with ECC in L2 cache (see Figure 2 again), this DDR3L ECC capability supports industrial Safety Integrity Level 3 (SIL 3). The i.MX 8X architecture also extends ECC support to external flash storage devices. Here, an integrated Bose, Ray-Chaudhuri, Hocquenghem (BCH) encoder and decoder module provides 62-bit ECC able to correct 2 to 20 single-bit errors within a block of data read from these storage devices.

Bringing up i.MX 8X-based applications

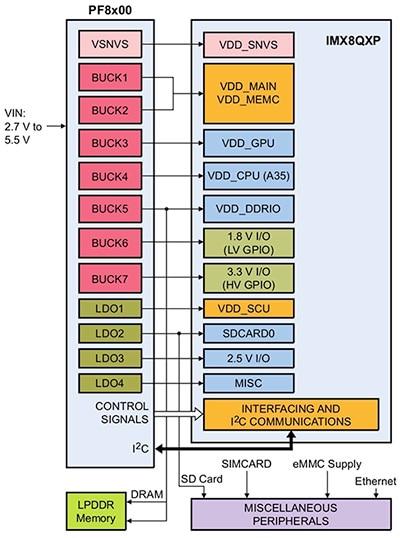

As with any processor in this class, implementing an i.MX 8X-based design requires careful attention to strict requirements for power, including critical power-up sequences. Powering up i.MX 8X devices requires bringing up power in sequence or simultaneously to four different supply groups, starting with the SVNS subsystem and continuing with the SCU, the I/Os and memory interfaces, and finally the remainder of the device. Developers can meet this requirement simply using NXP's PF8x00 power management integrated circuit (PMIC) devices, which provide a complete set of voltage rails and control signals needed to support i.MX 8X processors as well as external memory and typical system peripherals (Figure 5).

Figure 5: NXP PF8x00 PMICs provide a full set of voltage rails and control signals needed to power i.MX 8X processors. (Image source: NXP Semiconductors)

Figure 5: NXP PF8x00 PMICs provide a full set of voltage rails and control signals needed to power i.MX 8X processors. (Image source: NXP Semiconductors)

In implementing their own i.MX 8X-based designs, developers can use the NXP MC33PF8100CCES PMIC which is preprogrammed for use with 8QuadXPlus processors such as the MIMX8QX6AVLFZAC. Other PF8x00 variants such as the MC33PF8100A0ES and MC33PF8200A0ES support i.MX 8X processors but are not preprogrammed.

For safety applications, PF8200 series devices such as the MC33PF8200A0ES integrate features designed to support ASIL B systems. Along with multiple internal monitors including an output voltage monitor with a dedicated bandgap reference, PF8200 PMICs include a fail-safe output (FSOB) pin designed to keep the system in a safe state during power up or during a power failure event. In addition, an analog built in self-test (ABIST) routine tests all voltage monitors while a self-test routine verifies other device functionality.

Although PF8x00 PMICs can simplify hardware design of i.MX 8X-based systems, some developers may need to immediately begin evaluating i.MX 8X devices and rapidly prototype i.MX 8X-based applications. NXP’s MCIMX8QXP-CPU i.MX 8X Multisensory Enablement Kit (MEK) provides a ready development platform that combines an NXP i.MX 8QuadXPlus processor, NXP F8100 PMIC, 3 gigabyte (Gbyte) RAM, 32 Gbyte embedded Multi-Media Controller (eMMC) memory, and 64 megabyte (Mbyte) flash memory. Along with display, camera, and audio interfaces, the MEK board includes a set of sensors typically used in automotive or industrial applications. For additional connectivity, audio, and expansion options, developers can also add NXP’s optional MCIMX8-8X-BB baseboard.

Conclusion

For a growing number of applications such as automotive, industrial, building control and HMIs, processing workloads have expanded to include both traditional real-time I/O processing and emerging application level processing with multimedia graphics. Although design options exist for each type of workload, few available solutions meet the growing need for high performance, power efficient solutions able to satisfy requirements for safety certifiable designs in automotive and industrial applications.

As shown, using a family of multicore processors from NXP Semiconductors, developers can more effectively implement designs able to meet these diverse requirements and scale easily to address emerging requirements for high performance.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.